#### **Parts**

- 1. Preparation of a BRAVE Development Kit Environment

- 2. Development of a BRAVE Demonstrator Application

- 3. Open ESA FPGA Benchmark Suite

- 4. Radiation Test of a Xilinx Kintex-7 FPGA

### Git Repositories

- All projects are organized in Git repositories (TEC-EDM Git server)

- Projects are public → accessible within intranet

- BRAVE Development Kit Environment:

http://mars.ws.estec.esa.nl:8081/Lange/brave-dev-kit

BRAVE Demonstrator Application:

http://mars.ws.estec.esa.nl:8081/Lange/fmc-hdmi-cam

Open ESA FPGA Benchmark Suite:

https://gitrepos.estec.esa.int/FPGA/open-ESA-FPGA-benchmark-suite

Radiation Test of a Xilinx Kintex-7:

http://mars.ws.estec.esa.nl:8081/Lange/kintex-radiation-test

## Preparation of a BRAVE Development Kit Environment

Thomas Lange

29/08/2017

ESA UNCLASSIFIED - For Official Use

### BRAVE Development Kit Environment - Outline

- Motivation

- The BRAVE Development Kit

- **Development Environment**

- 4. Example Project/Demo

#### **Motivation**

- How to start a project with the BRAVE NG-Medium Development Kit?

- Creating a development environment as starting point by providing

- Documentation

- Automated design flow

- Small example project

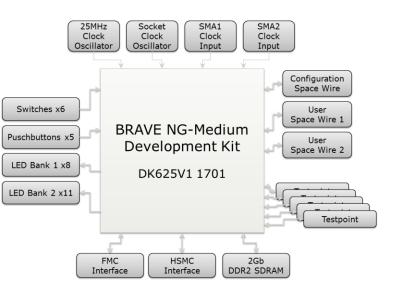

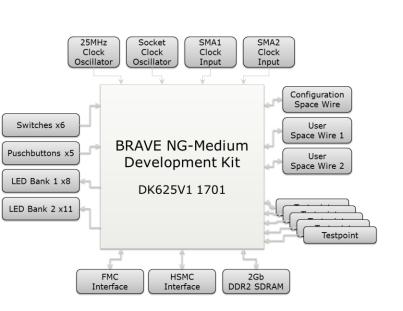

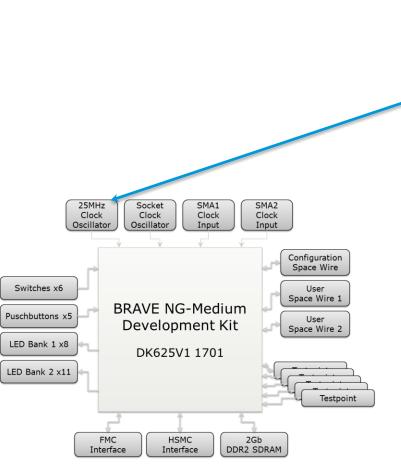

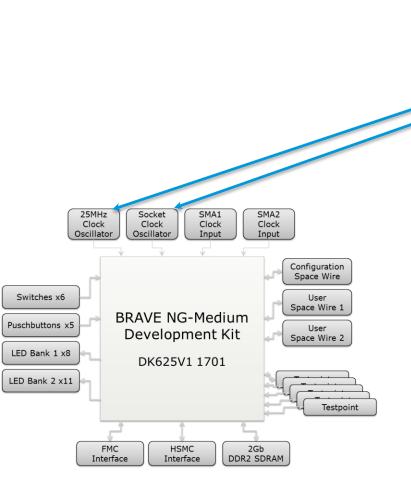

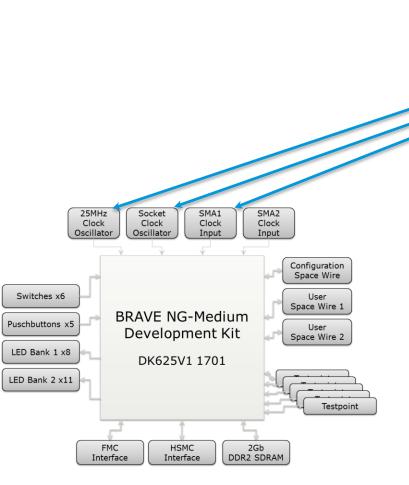

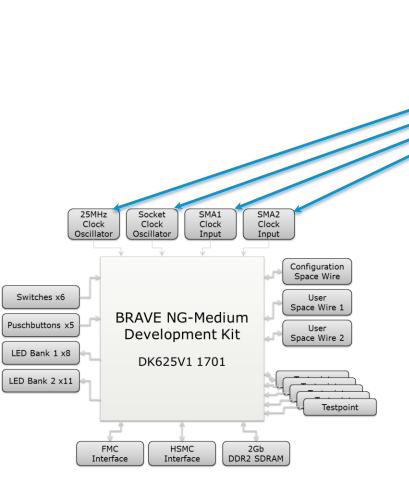

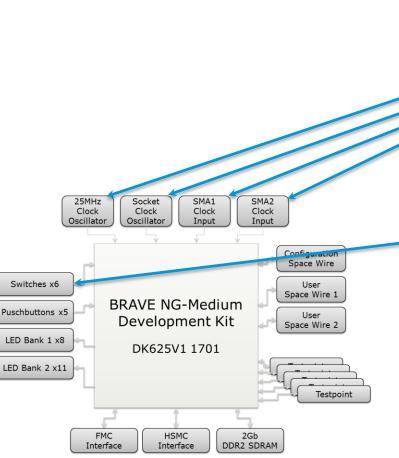

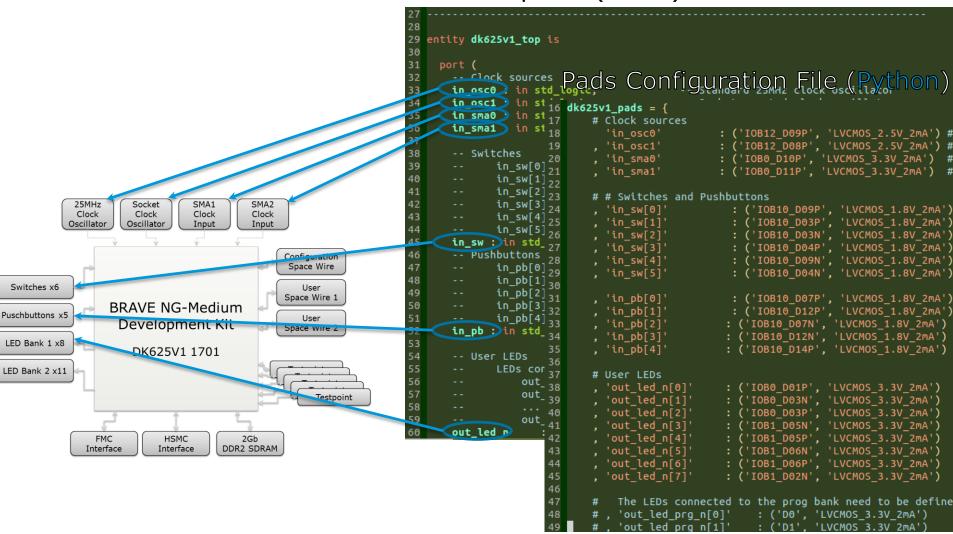

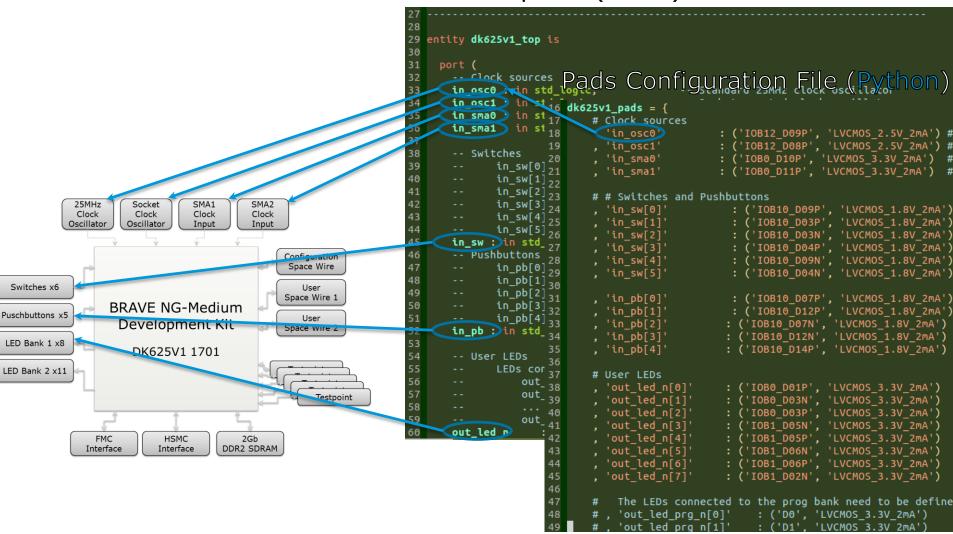

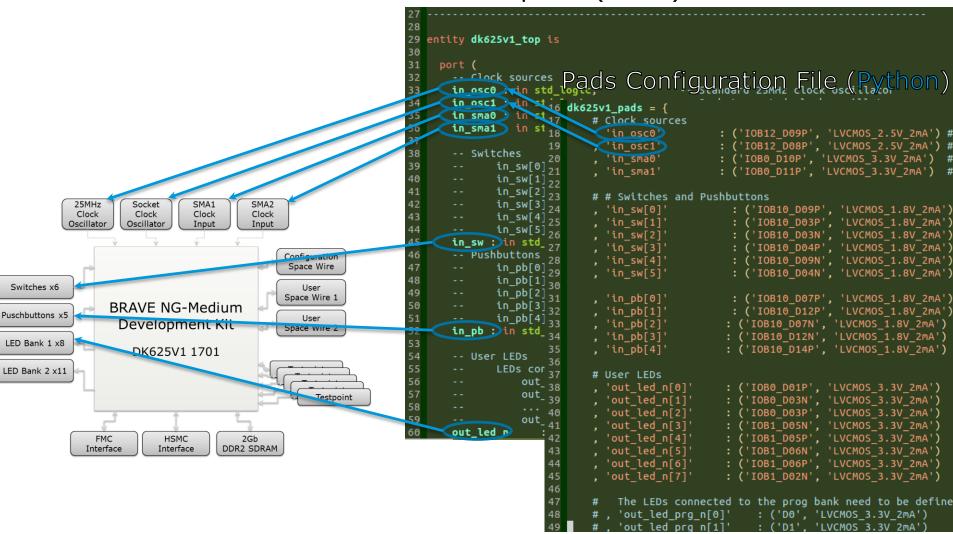

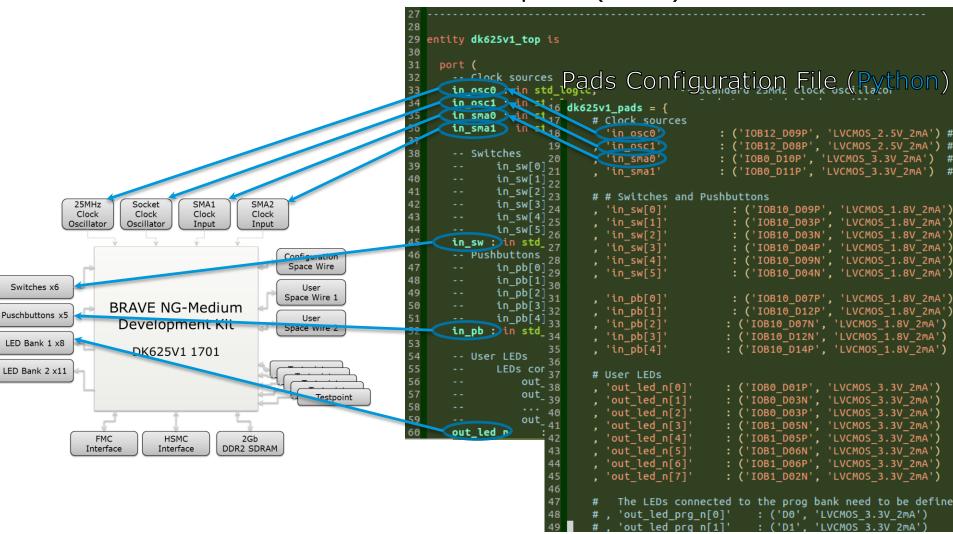

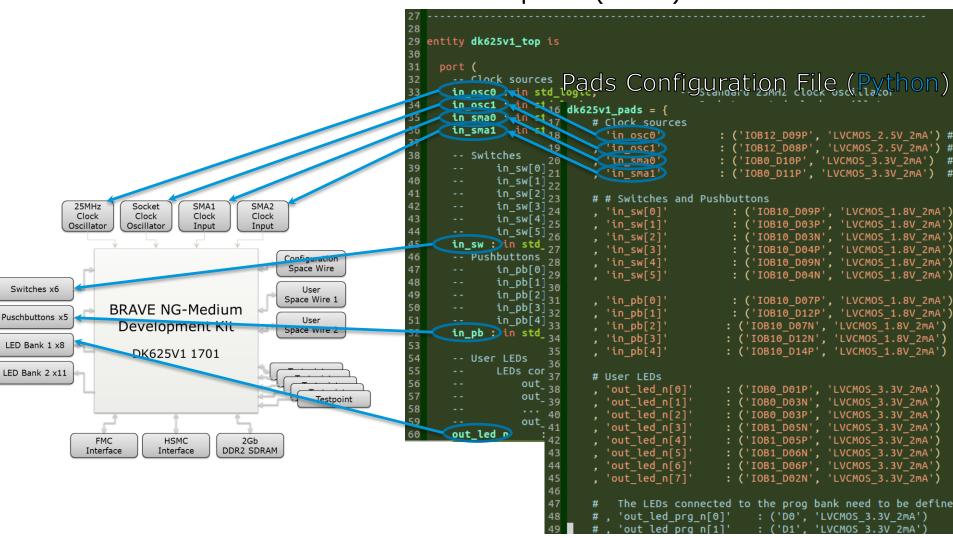

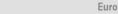

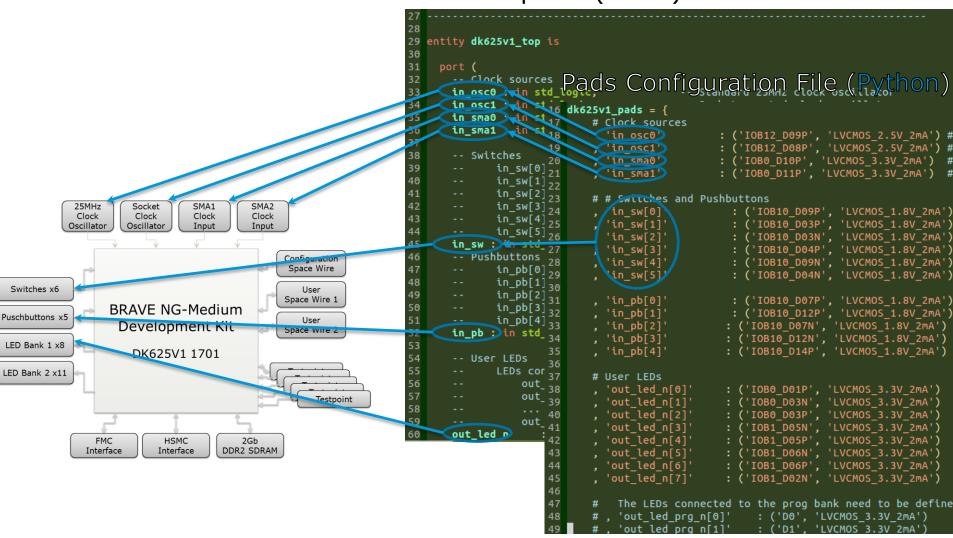

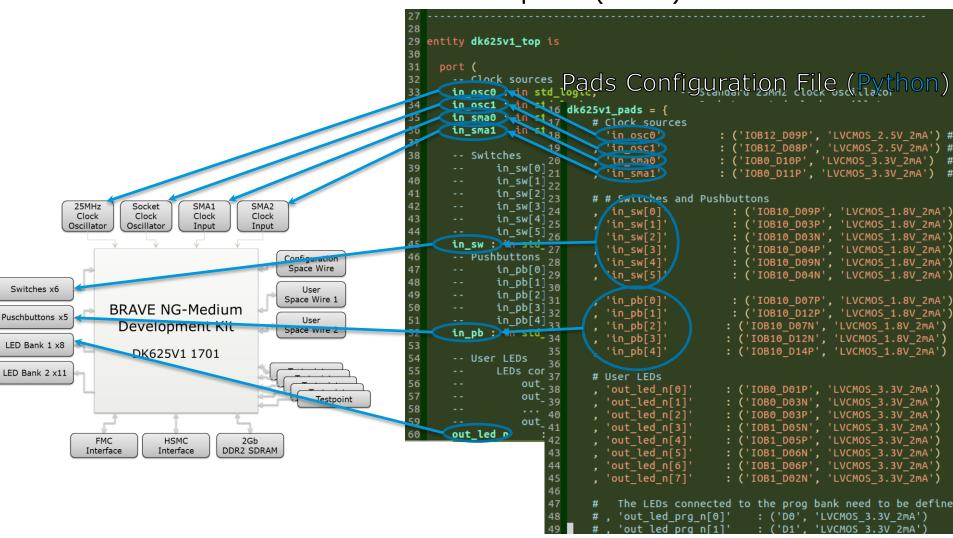

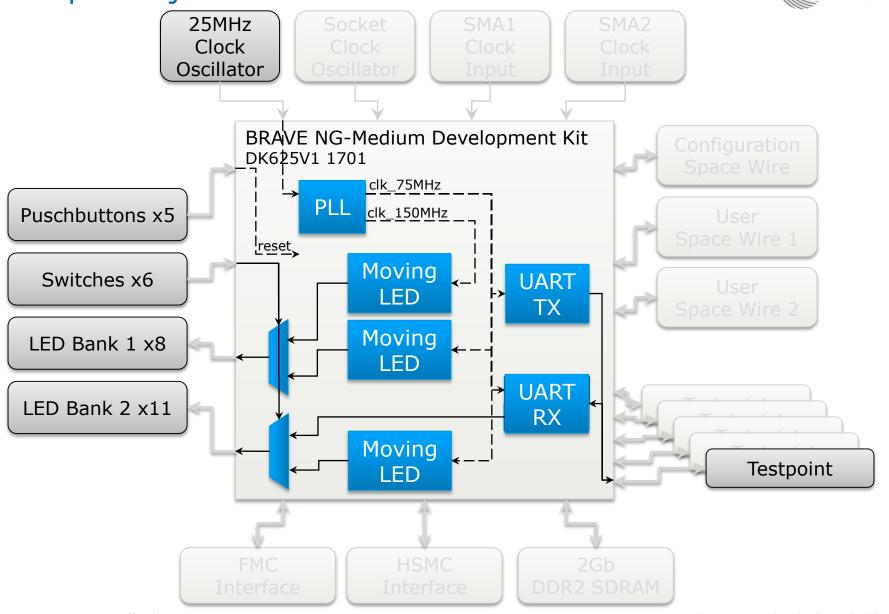

### The BRAVE Development Kit

25MHz Clock Oscillator

Socket Clock Oscillator SMA1 Clock Input SMA2 Clock Input

Switches x6

Puschbuttons x5

LED Bank 1 x8

LED Bank 2 x11

BRAVE NG-Medium Development Kit

DK625V1 1701

Configuration Space Wire

User Space Wire 1

User Space Wire 2

FMC Interface HSMC Interface 2Gb DDR2 SDRAM

ESA UNCLASSIFIED - For Official Use

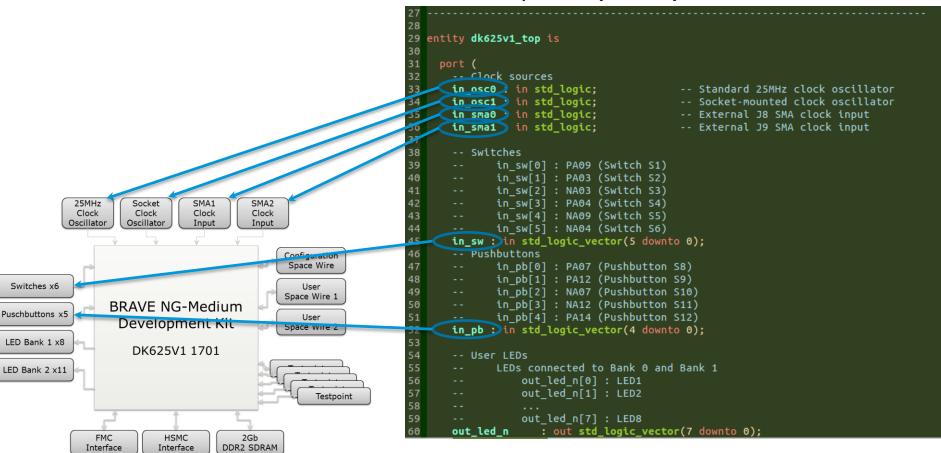

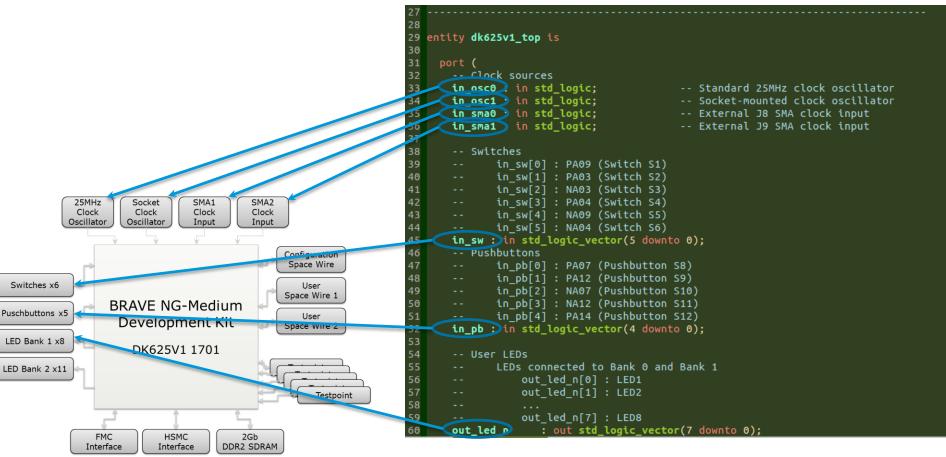

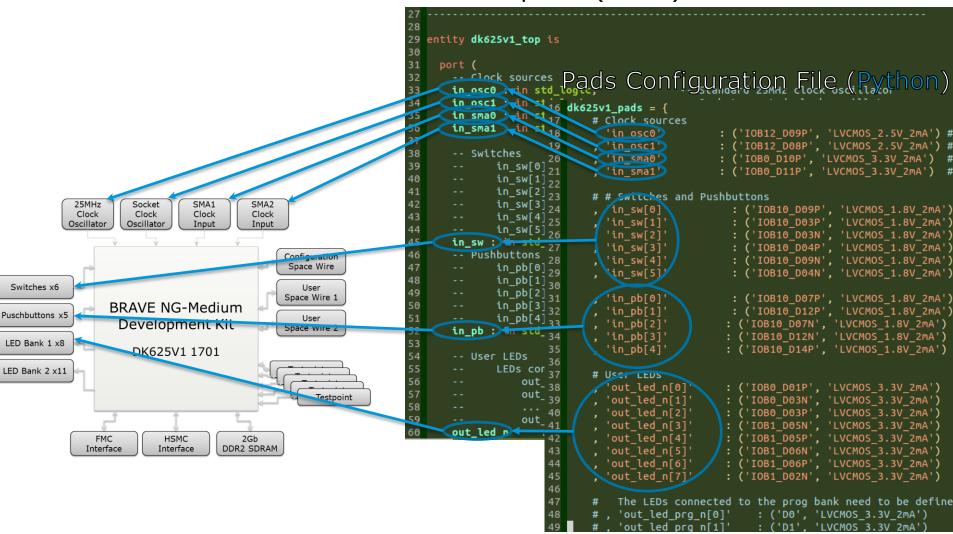

### **Development Environment**

- The development environment includes:

- Latest documentation by NanoXplore

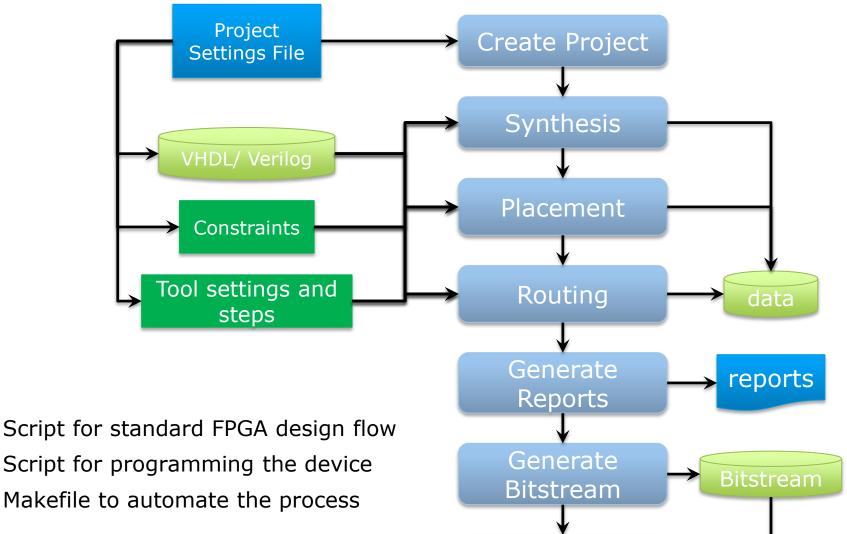

- Script to compile/synthesize a project

- Script to program the device

- Makefile which automates the complete process

- VHDL top module with corresponding pads configuration

- matches with available connectors on BRAVE Dev-Kit

- Example project

- Uses LEDs, switches, pushbuttons, PLL, testpoints (TP)

- Dedicated UART receiver and transmitter

### **Development Environment**

- The development environment includes:

- Latest documentation by NanoXplore

- Script to compile/synthesize a project

- Script to program the device

- Makefile which automates the complete process

- VHDL top module with corresponding pads configuration

- matches with available connectors on BRAVE Dev-Kit

- Example project

- Uses LEDs, switches, pushbuttons, PLL, testpoints (TP)

- Dedicated UART receiver and transmitter

### Development Environment – Flow automation

Program

device

ESA UNCLASSIFIED - For Official Use

### **Development Environment**

- The development environment includes:

- Latest documentation by NanoXplore

- Script to compile/synthesize a project

- Script to program the device

- Makefile which automates the complete process

- VHDL top module with corresponding pads configuration

- matches with available connectors on BRAVE Dev-Kit

- Example project

- Uses LEDs, switches, pushbuttons, PLL, testpoints (TP)

- Dedicated UART receiver and transmitter

#### Board Top File (VHDL)

```

entity dk625v1_top is

port (

-- Clock sources

in osc0 : in std logic;

-- Standard 25MHz clock oscillator

in osc1 : in std logic;

-- Socket-mounted clock oscillator

in_sma0 : in std_logic;

-- External J8 SMA clock input

in sma1 : in std logic;

-- External J9 SMA clock input

-- Switches

in_sw[0] : PA09 (Switch S1)

in sw[1] : PA03 (Switch S2)

in sw[2]: NA03 (Switch S3)

in sw[3] : PA04 (Switch S4)

in_sw[4] : NA09 (Switch S5)

in sw[5] : NA04 (Switch S6)

in_sw : in std_logic_vector(5 downto 0);

-- Pushbuttons

in_pb[0] : PA07 (Pushbutton S8)

in pb[1] : PA12 (Pushbutton S9)

in_pb[2] : NA07 (Pushbutton S10)

in_pb[3] : NA12 (Pushbutton S11)

in pb[4] : PA14 (Pushbutton S12)

in pb : in std logic vector(4 downto 0);

-- User LEDs

LEDs connected to Bank 0 and Bank 1

out led n[0] : LED1

out led n[1] : LED2

out_led_n[7] : LED8

out_led_n

: out std_logic_vector(7 downto 0);

```

ESA UNCLASSIFIED - For Official Use

```

entity dk625v1_top is

port (

-- Clock sources

-- Standard 25MHz clock oscillator

in_osc0 >> in std_logic;

in osc1 : in std logic;

-- Socket-mounted clock oscillator

in_sma0 : in std_logic;

-- External J8 SMA clock input

in sma1 : in std logic;

-- External J9 SMA clock input

-- Switches

in_sw[0] : PA09 (Switch S1)

in sw[1] : PA03 (Switch S2)

in sw[2]: NA03 (Switch S3)

in_sw[3] : PA04 (Switch S4)

in_sw[4] : NA09 (Switch S5)

in sw[5] : NA04 (Switch S6)

in_sw : in std_logic_vector(5 downto 0);

-- Pushbuttons

in_pb[0] : PA07 (Pushbutton S8)

in pb[1]: PA12 (Pushbutton S9)

in_pb[2] : NA07 (Pushbutton S10)

in_pb[3] : NA12 (Pushbutton S11)

in pb[4]: PA14 (Pushbutton S12)

in pb : in std logic vector(4 downto 0);

-- User LEDs

LEDs connected to Bank 0 and Bank 1

out led n[0] : LED1

out led n[1] : LED2

out_led_n[7] : LED8

out_led_n

: out std_logic_vector(7 downto 0);

```

```

entity dk625v1_top is

port (

-- Clock sources

in osc0    in std_logic;

-- Standard 25MHz clock oscillator

in osc1 > in std logic;

-- Socket-mounted clock oscillator

in_sma0 : in std_logic;

-- External J8 SMA clock input

in_sma1 : in std_logic;

-- External J9 SMA clock input

-- Switches

in_sw[0] : PA09 (Switch S1)

in sw[1] : PA03 (Switch S2)

in sw[2]: NA03 (Switch S3)

in_sw[3] : PA04 (Switch S4)

in_sw[4] : NA09 (Switch S5)

in sw[5] : NA04 (Switch S6)

in_sw : in std_logic_vector(5 downto 0);

-- Pushbuttons

in_pb[0] : PA07 (Pushbutton S8)

in pb[1]: PA12 (Pushbutton S9)

in_pb[2] : NA07 (Pushbutton S10)

in_pb[3] : NA12 (Pushbutton S11)

in pb[4]: PA14 (Pushbutton S12)

in pb : in std logic vector(4 downto 0);

-- User LEDs

LEDs connected to Bank 0 and Bank 1

out led n[0] : LED1

out led n[1] : LED2

out_led_n[7] : LED8

out_led_n

: out std_logic_vector(7 downto 0);

```

```

entity dk625v1_top is

port (

-- Clock sources

in osc0 in std logic:

-- Standard 25MHz clock oscillator

in osc1 ) in std logic;

-- Socket-mounted clock oscillator

in_sma0 > in std_logic;

-- External J8 SMA clock input

in sma1 : in std logic;

-- External J9 SMA clock input

-- Switches

in_sw[0] : PA09 (Switch S1)

in sw[1] : PA03 (Switch S2)

in sw[2]: NA03 (Switch S3)

in_sw[3] : PA04 (Switch S4)

in_sw[4] : NA09 (Switch S5)

in sw[5] : NA04 (Switch S6)

in_sw : in std_logic_vector(5 downto 0);

-- Pushbuttons

in_pb[0] : PA07 (Pushbutton S8)

in pb[1]: PA12 (Pushbutton S9)

in_pb[2] : NA07 (Pushbutton S10)

in_pb[3] : NA12 (Pushbutton S11)

in pb[4]: PA14 (Pushbutton S12)

in pb : in std logic vector(4 downto 0);

-- User LEDs

LEDs connected to Bank 0 and Bank 1

out led n[0] : LED1

out led n[1] : LED2

out_led_n[7] : LED8

out_led_n

: out std_logic_vector(7 downto 0);

```

```

entity dk625v1_top is

port (

-- Clock sources

in osc0 ? in std_logic;

-- Standard 25MHz clock oscillator

-- Socket-mounted clock oscillator

in osc1 > in std logic;

in sma0 > in std_logic;

-- External J8 SMA clock input

in_sma1 in std_logic;

-- External J9 SMA clock input

-- Switches

in_sw[0] : PA09 (Switch S1)

in sw[1] : PA03 (Switch S2)

in sw[2]: NA03 (Switch S3)

in_sw[3] : PA04 (Switch S4)

in_sw[4] : NA09 (Switch S5)

in sw[5] : NA04 (Switch S6)

in_sw : in std_logic_vector(5 downto 0);

-- Pushbuttons

in_pb[0] : PA07 (Pushbutton S8)

in pb[1]: PA12 (Pushbutton S9)

in_pb[2] : NA07 (Pushbutton S10)

in_pb[3] : NA12 (Pushbutton S11)

in pb[4]: PA14 (Pushbutton S12)

in pb : in std logic vector(4 downto 0);

-- User LEDs

LEDs connected to Bank 0 and Bank 1

out led n[0] : LED1

out led n[1] : LED2

out_led_n[7] : LED8

out_led_n

: out std_logic_vector(7 downto 0);

```

```

entity dk625v1_top is

port (

-- Clock sources

in osc0 ? in std_logic;

-- Standard 25MHz clock oscillator

in osc1 ) in std logic;

-- Socket-mounted clock oscillator

in sma0 > in std_logic;

-- External J8 SMA clock input

in_sma1 in std_logic;

-- External J9 SMA clock input

-- Switches

in_sw[0] : PA09 (Switch S1)

in sw[1] : PA03 (Switch S2)

in sw[2]: NA03 (Switch S3)

in_sw[3] : PA04 (Switch S4)

in_sw[4] : NA09 (Switch S5)

in sw[5] : NA04 (Switch S6)

in_sw : in std_logic_vector(5 downto 0);

-- Pushbuttons

in_pb[0] : PA07 (Pushbutton S8)

in pb[1]: PA12 (Pushbutton S9)

in_pb[2] : NA07 (Pushbutton S10)

in pb[3]: NA12 (Pushbutton S11)

in pb[4]: PA14 (Pushbutton S12)

in pb : in std logic vector(4 downto 0);

-- User LEDs

LEDs connected to Bank 0 and Bank 1

out led n[0] : LED1

out led n[1] : LED2

out_led_n[7] : LED8

out_led_n

: out std_logic_vector(7 downto 0);

```

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

#### Board Top File (VHDL)

ESA UNCLASSIFIED - For Official Use

Thomas Lange | 29/08/2017 | Slide 28

European Space Agency

### **Development Environment**

- The development environment includes:

- Latest documentation by NanoXplore

- Script to compile/synthesize a project

- Script to program the device

- Makefile which automates the complete process

- VHDL top module with corresponding pads configuration

- matches with available connectors on BRAVE Dev-Kit

- Example project

- Uses LEDs, switches, pushbuttons, PLL, testpoints (TP)

- Dedicated UART receiver and transmitter

### **Example Project**

ESA UNCLASSIFIED - For Official Use

# Demo

### Questions?

# Development of a BRAVE Demonstrator Application

Thomas Lange

29/08/2017

ESA UNCLASSIFIED - For Official Use

### **BRAVE Demonstrator Application - Outline**

- 1. Motivation

- FMC-HDMI-CAM Daughterboard

- 3. Development Process

- 4. Demo

- 5. Summary of Development Status

- 6. Future Work

### **Motivation**

- Development of a demonstrator application for the BRAVE NG-Medium

- Gets the easily attention

- Image/Video application

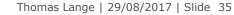

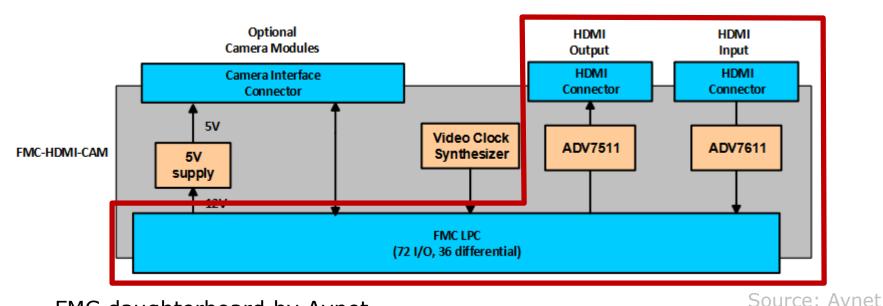

### FMC-HDMI-CAM Daughterboard

- FMC daughterboard by Avnet

- Using the FMC connector (mezzanine card interface)

- HDMI Input (based on ADI ADV6711)

- HDMI Output (based on ADI ADV7511)

- Video Clock Synthesizer (based on TI CDCE913)

- Camera Interface (for camera modules)

- Avnet provides reference design (<a href="https://github.com/Avnet/hdl">https://github.com/Avnet/hdl</a>)

= 11

ESA UNCLASSIFIED - For Official Use

**European Space Agency**

Source: Avnet

#### FMC-HDMI-CAM Daughterboard

- FMC daughterboard by Avnet

- Using the FMC connector (mezzanine card interface)

- HDMI Input (based on ADI ADV6711)

- HDMI Output (based on ADI ADV7511)

- Video Clock Synthesizer (based on TI CDCE913)

- Camera Interface (for camera modules)

- Avnet provides reference design (<a href="https://github.com/Avnet/hdl">https://github.com/Avnet/hdl</a>)

= 11 1

ESA UNCLASSIFIED - For Official Use

Thomas Lange | 29/08/2017 | Slide 37

**European Space Agency**

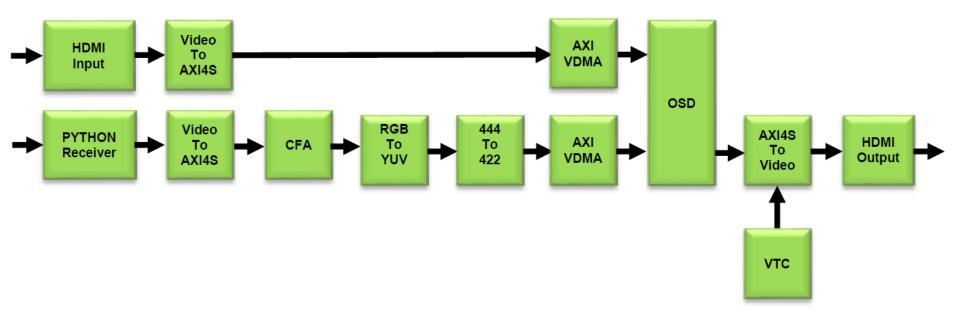

# FMC-HDMI-CAM Daughterboard – Reference design

Source: Avnet

- Reference design supports Zync-Board or ZedBoard

- Technology dependent HDL code

- Some of the used IP cores need licenses

- I2C configuration of HDMI in-/output chips through embedded ARM core

#### **Development Process**

- Design porting issues:

- I2C configuration of HDMI chips is done by embedded ARM core

- BRAVE NG-Medium does not provide hard-wired processor

- Technology dependent HDL code

- Some of the used IP cores need licenses

- Development steps:

- Simplify design → no licenses for IP cores needed

- Porting to Xilinx 7-Series FPGA (Kintex-7 KC705)

- Integrate dedicated I2C IP core

- Identify required I2C messages

- Porting to Microsemi RTG4 Dev-Kit

- Rewrite HDL code technology independent

- Porting to NanoXplore BRAVE NG-Medium DK625V1

- Handle not yet supported features

- Handle issues of current tool versions

# Demo

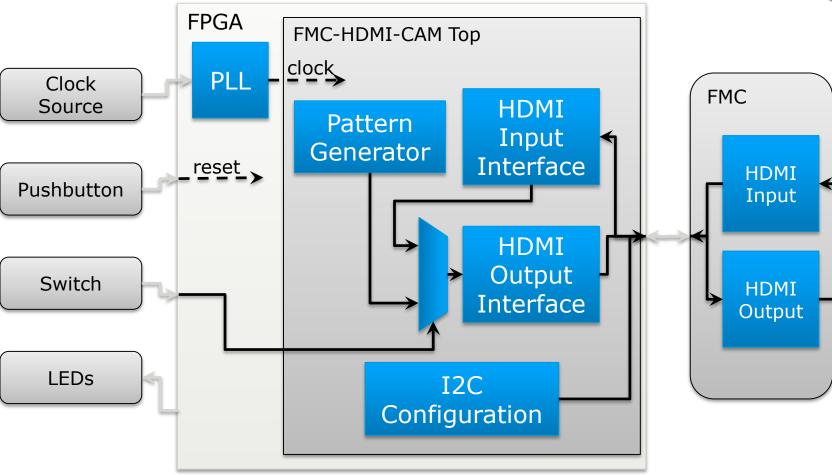

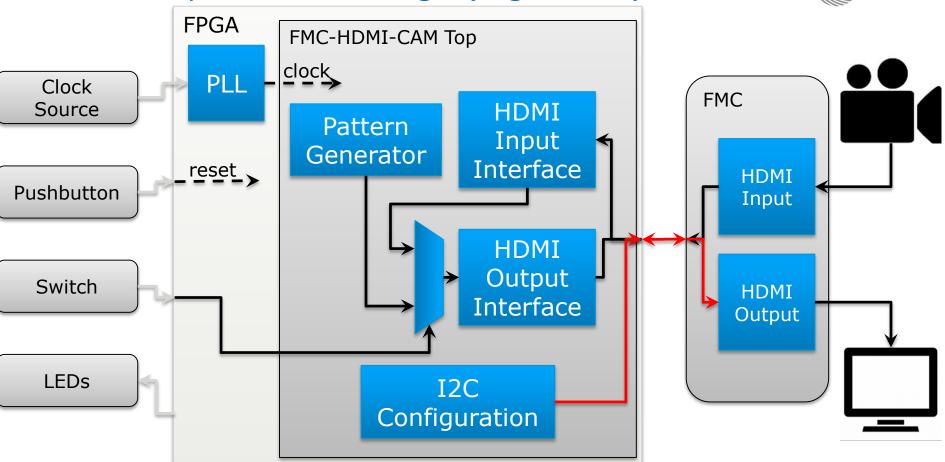

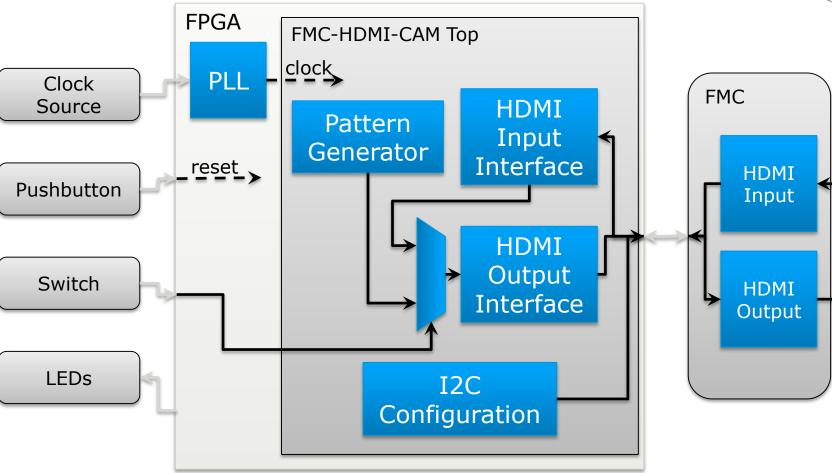

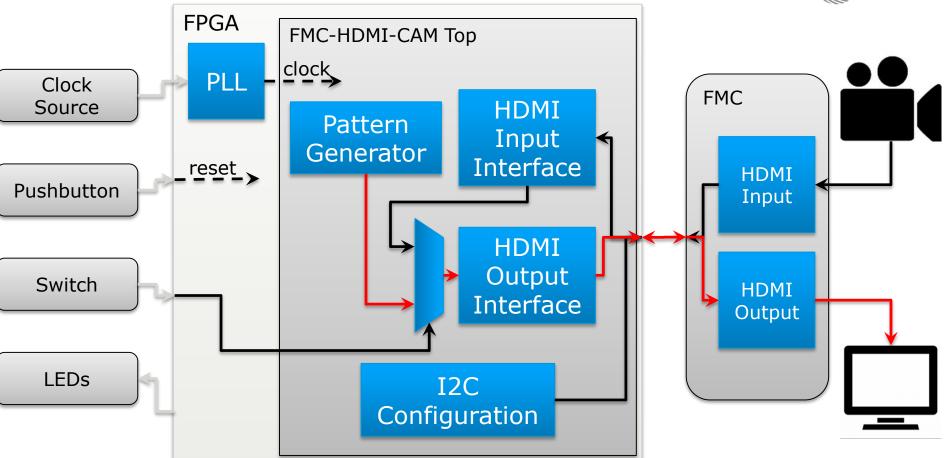

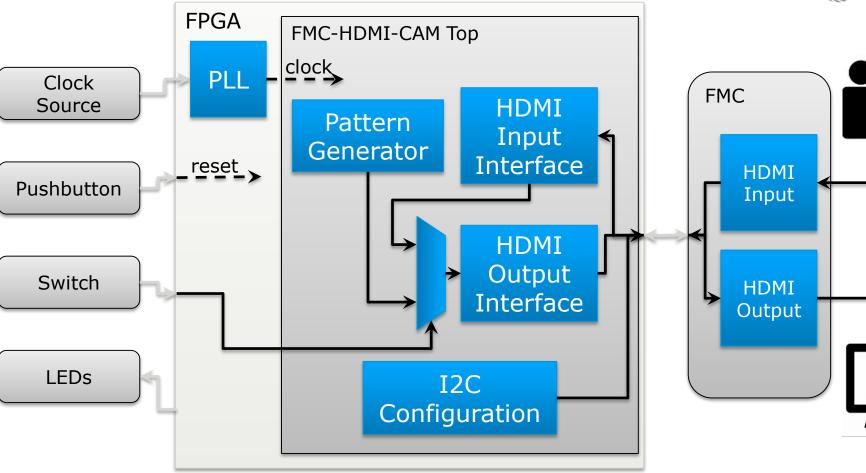

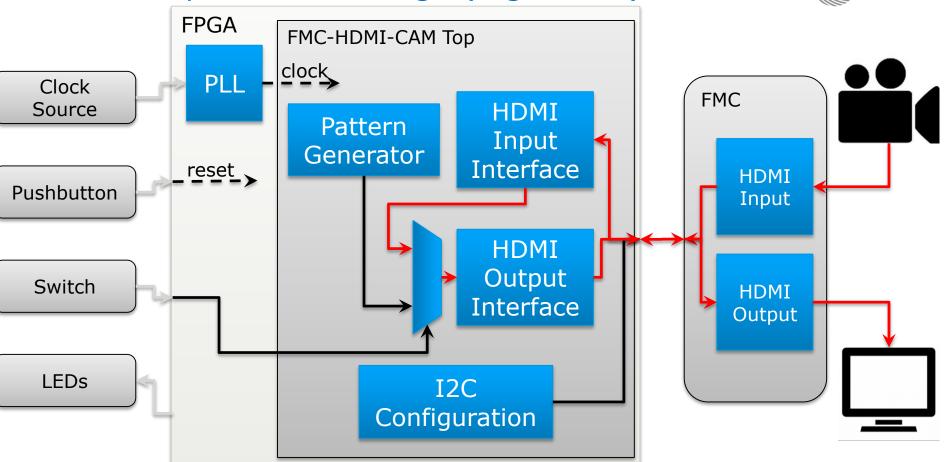

- Technology independent design (FMC-HDMI-CAM Top)

- Configuration via dedicated I2C master

- HDMI Output stream with Video Pattern Generator

- HDMI In-/Output stream pass through

ESA UNCLASSIFIED - For Official Use

- Technology independent design (FMC-HDMI-CAM Top)

- Configuration via dedicated I2C master

- HDMI Output stream with Video Pattern Generator

- HDMI In-/Output stream pass through

- Configuration via dedicated I2C master

- HDMI Output stream with Video Pattern Generator

- HDMI In-/Output stream pass through

- Technology independent design (FMC-HDMI-CAM Top)

- Configuration via dedicated I2C master

- HDMI Output stream with Video Pattern Generator

- HDMI In-/Output stream pass through

- Technology independent design (FMC-HDMI-CAM Top)

- Configuration via dedicated I2C master

- HDMI Output stream with Video Pattern Generator

- HDMI In-/Output stream pass through

ESA UNCLASSIFIED - For Official Use

- Technology independent design (FMC-HDMI-CAM Top)

- Configuration via dedicated I2C master

- HDMI Output stream with Video Pattern Generator

- HDMI In-/Output stream pass through

ESA UNCLASSIFIED - For Official Use

#### Summary of Development Status

- HDMI In-/Output interface is technology independent

- Dedicated I2C Master core is implemented

- Configuration of HDMI In-/Output through I2C

- Video Pattern Generator is implemented

- Xilinx Kintex-7 KC705:

- HDMI Output with pattern generator

- HDMI Input HDMI Output pass through

- Microsemi RTG4 Dev-Kit:

- HDMI Output with pattern generator

- NanoXplore BRAVE NG-Medium DK625V1:

- HDMI Output with pattern generator (with artefacts)

#### Future Work

- Continue porting to BRAVE NG-Medium Dev-Kit

- Probably solved with new release of the tool

- Implementation of actual image/video application by Klemen Bravhar

- Usage of MATLAB HDL coder

# Questions?

# Open ESA FPGA Benchmark Suite

Thomas Lange, David Merodio Codinachs

29/08/2017

## Open ESA FPGA Benchmark Suite - Outline

- Motivation

- Methodology

- 3. Open ESA FPGA Benchmark Suite Overview

- 4. Benchmark Circuits

- 5. Public Availability

- 6. Current Development Status

- 7. Conclusion

#### **Motivation**

- The offer of FPGAs for space is increasing; as well as their complexity

- FPGAs have different architectures and tools

- No industry standard for benchmarking PLDs (as it exists for CPUs)

- Difficult to chose devices for given application

- FPGAs are very versatile

- → A flexible benchmark environment is needed which

- addresses many aspects

- can be modified for specific purposes

- → Large companies have internal benchmarks, methodology and automation. Universities, research institutes and smaller companies might benefit from the benchmarks, data and automation sharing.

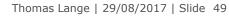

#### Methodology

- The benchmark environment automates the standard FPGA design flow

- The steps are performed on several devices by using the corresponding CAD tools

After each step in the design flow the parameters are extracted and

ESA UNCLASSIFIED - For Official Use

#### Open ESA FPGA Benchmark Suite - Overview

ESA UNCLASSIFIED - For Official Use

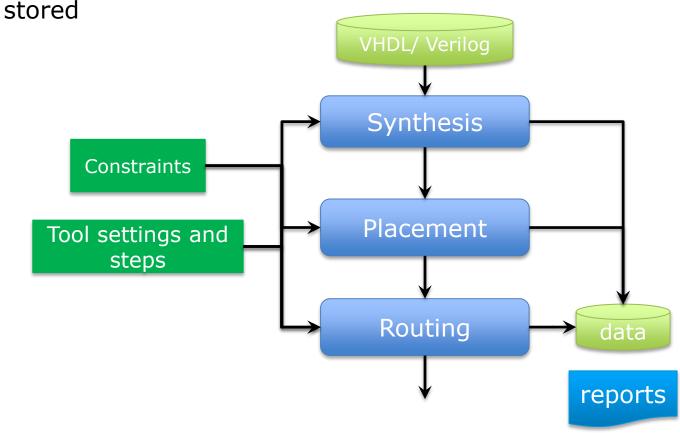

#### Open ESA FPGA Benchmark Suite - Overview

- The Open ESA FPGA Benchmark Suite consists of

- Benchmark circuits (VHDL)

- CAD tool specific design flow scripts (TCL)

- Benchmark Environment (Python)

- Configuration Files (JSON)

- The device parameters are currently (can be extended):

- logic capacity

- speed performance

- power

- The current CAD tool parameters are (can be extended):

- compile time

- memory usage

#### **Public Availability**

The benchmark environment is organized in a Git repository

https://gitrepos.estec.esa.int/FPGA/open-ESA-FPGA-benchmark-suite.git

- The availability to the public enables

- Experience can be shared

- the possibility to add and modify circuits for own purposes, e.g.

- add new circuits which address different architectural features

- the possibility to add and modify design flows, e.g.

- add design flow with special constraints

- add design flow with different CAD tool settings/versions

- add design flow for new CAD tools

The use and collaboration of the suite is highly encouraged!

= 11 🛌

#### Design flow configuration example

#### Example of design flow configuration (designFlowSettings.json):

```

Flow name

1

Shell command

"ISE 13.2";

2

"shellCLI"

: "xtclsh",

3

"toolSetup": "tools/xilinx/ise13.2_64_env.csh",

Script to create

4

"createPrj" : "tools/xilinx/new_ise_project.tcl",

5

the Project

"synPrj"

: "tools/xilinx/syn_ise.tcl"

},

"ISE 14.7": {

8

Script to perform

"shellCLI" : "xtclsh",

9

"toolSetup": "tools/xilinx/ise14.7_64_env.csh",

Synthesis, Place &

10

"createPrj" : "tools/xilinx/new_ise_project.tcl",

11

Route

"synPrj"

: "tools/xilinx/syn ise.tcl"

12

},

13

"Libero SoC 11.7": {

14

"shellCLI" : "libero".

15

Scripts to setup

"toolSetup" :

16

"tools/microsemi/libero_env.csh",

17

the tools

"tools/microsemi/synopsys env.csh"

18

19

"createPrj": "tools/microsemi/new libero project.tcl",

20

: "tools/microsemi/syn libero.tcl"

"synPrj"

21

22

23

```

ESA UNCLASSIFIED - For Official Use

#### Device configuration example

```

1

"Virtex-5QV"

2

"tools": "ISE 13.2"

3

"deviceSpec" : {

4

"family": "Virtex-5QV",

5

: "xqr5vfx130",

"die"

6

"package" : "cf1752",

"speed"

: "-1",

8

9

},

10

"Kintex-7" : {

11

"tools" : [

12

"ISE 13.2"

13

"ISE 14.7"

14

15

"deviceSpec" : {

16

"family": "Kintex7",

17

"die" : "xc7k70t",

18

"package": "fbg676",

19

"speed" : "-3",

20

21

},

22

"RTG4"

: "Libero SoC 11.7",

"tools"

24

"deviceSpec" : {

25

"family" : "RTG4",

26

"die"

: "RT4G150",

27

"package" : "1657 CG",

28

"speed"

: "STD",

29

"dieVoltage" : "1.2"

30

31

32

33

```

Example of device configuration (deviceSettings.json):

Device name

Flow names (see previous slide)

Device definition

ESA UNCLASSIFIED - For Official Use

#### Project configuration example

#### Example of project configuration (prjSettings.json):

```

1

2

"hdlFiles" : [

3

".../.../utils/hdl/io ff.vhd",

4

"../../utils/hdl/io_reg.vhd",

5

".../.../utils/hdl/utils.vhd",

6

"../../utils/hdl/reduce_pack.vhd",

7

"./hdl/generic_logic_gate.vhd"

8

9

"vhdlVersion": "VHDL1993"

10

11

```

Project name created by the **FPGA** tool

#### Benchmark execution example

- Steps to execute the benchmark:

- 1. Initialize the environment

```

$ source utilities/set_env.sh # use with Bash shell

$ source utilities/set_env.csh # use with C shell

```

2. Got to work directory

```

$ cd circuits/basic/generic_logic_gate/

```

- 3. Run the benchmark

- \$ ./benchmark\_generic\_logic\_gate.py

```

Output during execution

```

ESA UNCLASSIFIED - For Official Use

#### **Benchmark Circuits**

- Initial set of benchmark circuits provided

- inspired by PREP, ITC'99 and IWLS benchmark suites

- Small designs which address only particular architectural features

- LUTs

- DSP-blocks

- carry propagation logic

- memory cells

- More complex circuits which represent common arithmetic functions

- e.g. Adder Tree, CORDIC, Moving Average Filter, UART (FSM), ...

- resource usage and performance can be estimated for real designs

- The number of benchmark circuits is expected to grow

#### **Current Development Status**

- The repository includes an initial set of benchmark circuits

- The integrated CAD tools currently included:

- Xilinx ISE

- Microsemi Libero

- Ongoing:

- Integration of further CAD tools (NanoXmap)

- Automation to parse reports of the tools to extract parameters

#### Conclusion

- The Open ESA FPGA Benchmark Suite

- enables acquire experience of FPGAs by different vendors and their CAD tools

- is publicly available

- transparent results

- has an "open interface"

- integration and modification of additional benchmark circuits, FPGAs and CAD tools is possible

#### References

- 1. D. McCarty, D. Faria, and P. Alfke, "PREP Benchmarks for Programmable Logic Devices" in Custom Integrated Circuits Conference, 1993., Proceedings of the IEEE 1993, pp. 7.7.1–7.7.6, May 1993.

- 2. F. Corno, M. S. Reorda, and G. Squillero, "RT-level ITC'99 benchmarks and first ATPG results" IEEE Design Test of Computers, vol. 17, pp. 44–53, Jul 2000.

- 3. "White Paper: Guidance for Accurately Benchmarking FPGAs" tech. rep., Altera Corporation, Dec 2007.

- 4. S. Kliman, "PREP Benchmarks Reveal Performance and Capacity Tradeoffs of Programmable Logic Devices" in Proceedings Seventh Annual IEEE International ASIC Conference and Exhibit, pp. 376–382, Sep 1994.

- 5. "White Paper: FPGA Performance Benchmarking Methodology" tech. rep., Altera Corporation, Aug 2007.

- 6. C. Albrecht, "IWLS 2005 Benchmarks." Online: http://iwls.org/iwls2005/benchmark presentation.pdf (accesed March 2017), Jun 2005.

#### Radiation test of a Xilinx Kintex-7 - Outline

- Motivation

- 2. Test Set-Up

- 3. Device Under Test

- 4. Summary Test Results

#### Motivation

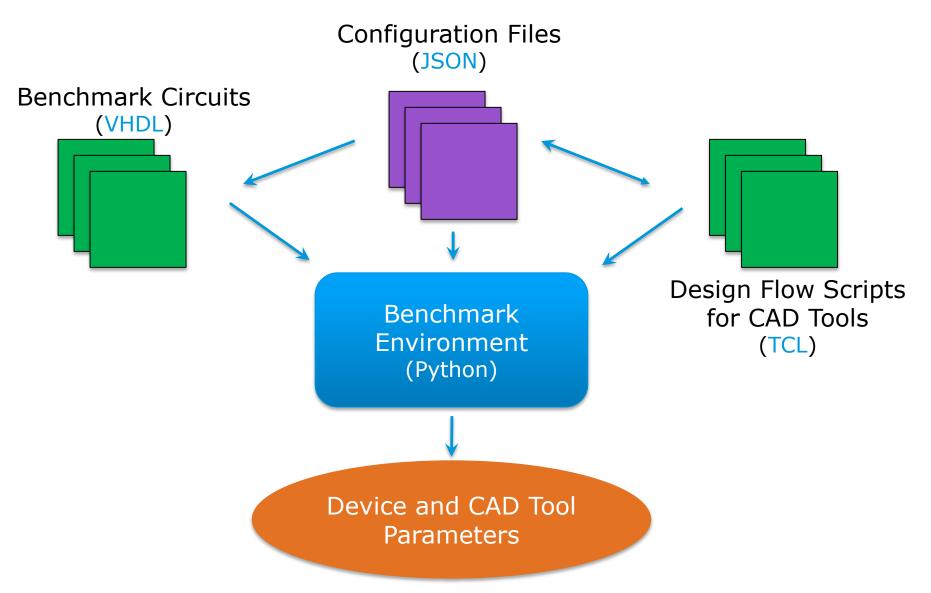

- Singe Event Effects (SEE) characterization is used to predict design error rates

- Radiation test experiments common test methodology is shift register based

- Methodology issue: not close to real designs

- Implementation of more complex designs with

- Logic cones at inputs and outputs of Flip Flops

- Realistic combinatorial stages between Flip Flops

- Radiation test of a Kintex-7 by TRAD

- Irradiation was performed at RADEF with not tilted heavy ions

# Shift Register Chain

Source: M. Bera

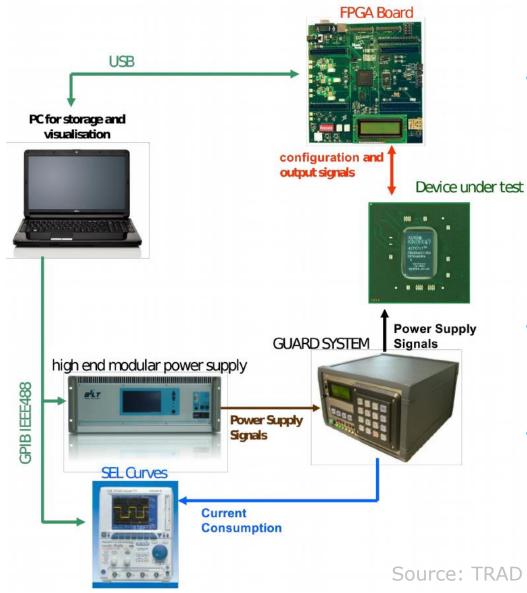

#### Test Set-Up

- Evaluate SEE sensitivity of Xilinx 7-Series FPGA

- Single Event Latch-Up (SEL)

- Single Event Upset (SEU)

- Multi-Bit Upset (MBU)

- Single Event Functional Interrupt (SEFI)

- Maximum used LET: 60.0 MeV.cm<sup>2</sup>/mg

- Test Vehicles:

- Shift Register

- Block Memory

- ESA dedicated design

ESA UNCLASSIFIED - For Official Use

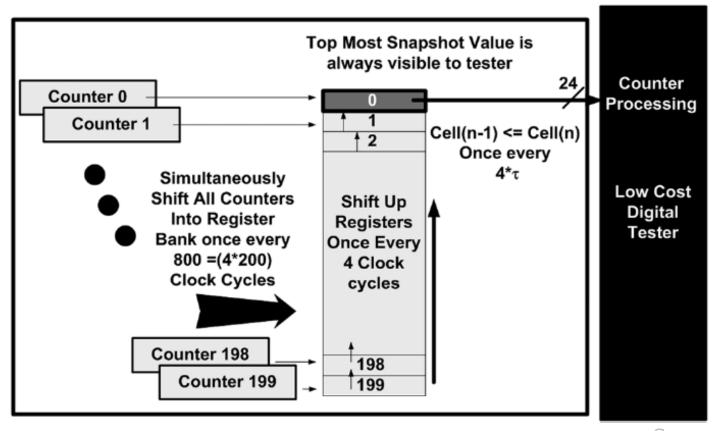

#### Device Under Test – Independent Counter Array

Source: M. Berg

- Design proposed by Melanie Berg, NASA/GSFC

- "SEU Analysis of Complex Circuits Implemented in Actel RTAX-S FPGA"

- Aim: increase complexity

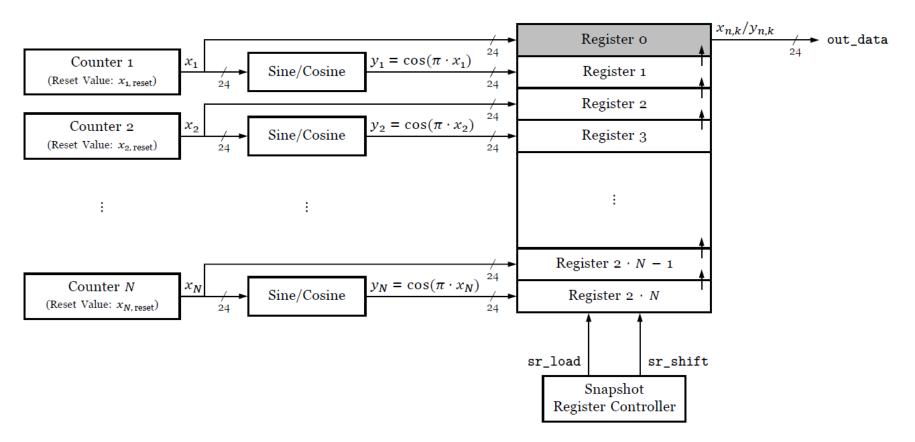

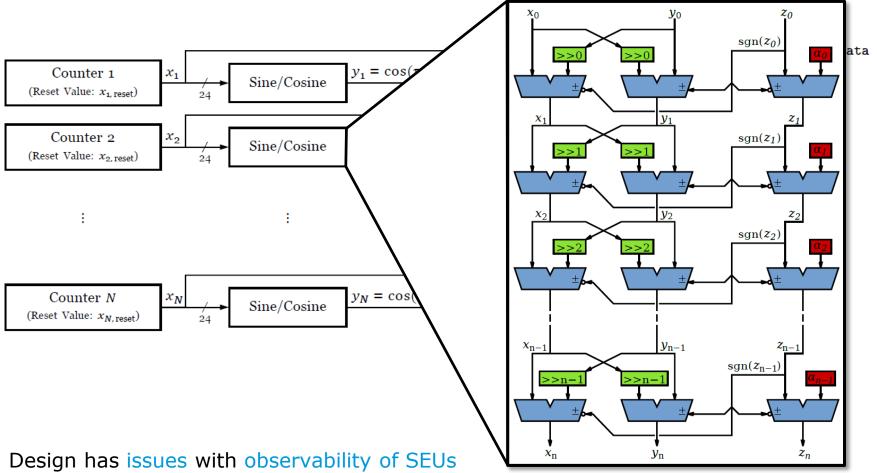

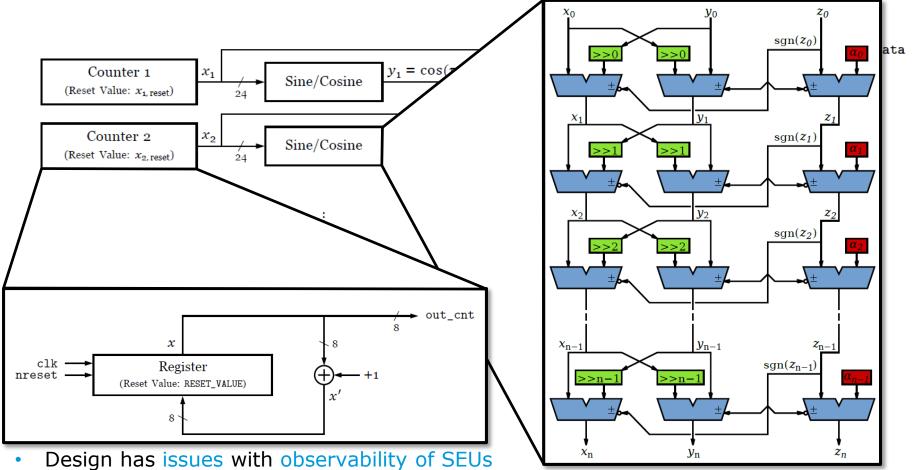

#### Device Under Test - High Level Description

- Extension of Independent Counter Array by adding sine/cosine calculation

- Sine/Cosine calculation is based on CORDIC

- Sine/Cosine can also be calculated by using LUT + multiplication

- Evaluation of hard-wired multipliers (DSP blocks)

\_\_\_\_\_

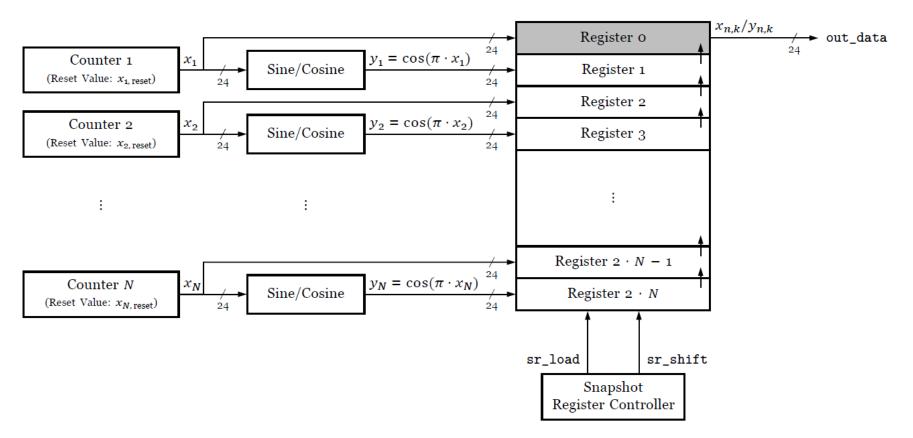

#### Device Under Test – Observability Issues

- Design has issues with observability of SEUs

- SEU in cosine calculation might not be captured by the snapshot register

- Not recognized in tester

- Feedback loop needed

- Step back to original Independent Counter Array

Device Under Test – Observability Issues

- SEU in cosine calculation might not be captured by the snapshot register

- Not recognized in tester

- Feedback loop needed

- Step back to original Independent Counter Array

ESA UNCLASSIFIED - For Official Use

#### Device Under Test – Observability Issues

- SEU in cosine calculation might not be captured by the snapshot register

- Not recognized in tester

- Feedback loop needed

- Step back to original Independent Counter Array

ESA UNCLASSIFIED - For Official Use

#### **Summary Test Results**

SEUs, MBUs and SEFIs were observed at minimum LET of 1.83 MeV.cm<sup>2</sup>/mg

#### References

1. M. Berg, H. Kim, M. Friendlich, C. Perez, C. Seidleck, K. LaBel and R. Ladbury, "SEU Analysis of Complex Circuits Implemented in Actel RTAX-S FPGA Devices" in IEEE Transaction on Nuclear Science, 2011., pp. 1015–1022, June 2011.

# **Questions?**